R.F. Note #123 NSCL November 17, 2003

John Vincent Mark Davis Brian Drewyor Mike Holcomb

# **NSCL Cyclotron RF Phase Control System**

| INTRODUCTION                      | 2  |

|-----------------------------------|----|

| SIGNAL FLOW                       | 3  |

| MODULE SPECIFICATIONS             | 4  |

| SUMMARY AND CONCLUDING STATEMENTS | 12 |

# Introduction

The signal distribution and phase control system of the NSCL rf systems has been upgraded. A common set of modules is used for the cyclotrons and injection line bunchers. The upgrade is significant because it provides for 1) full 360 degree phase control, 2) reducing the module count from 28 to 8, 3) replacing obsolete integrated circuits with modern ones, 4) improving both the rf and control signal quality, and 5) increasing the reliability by uncoupling phase control issues from degrading the tuning requirements. The upgrade also begins a transition from analog control interfaces to digital control interfaces. The Phase Regulation module is the first module with these capabilities and allows for both full local and remote control. The system is fully documented in the NSCL Electronics Department bundle #162.

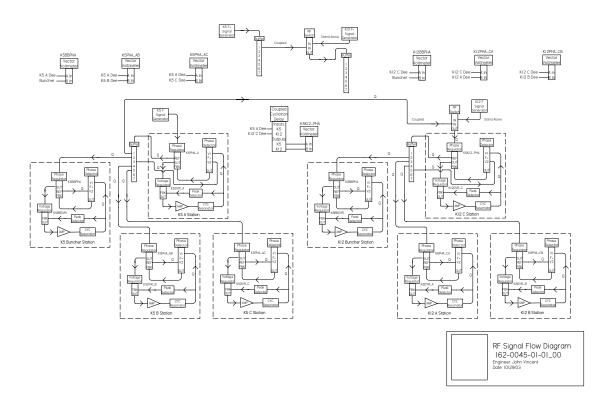

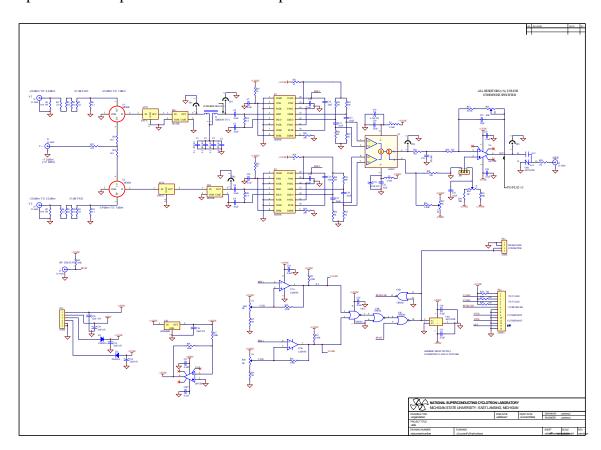

Figure 1 Overall RF Signal Flow: # 162-0045-01-01\_00

## Signal Flow

The rf signal flow has been changed as a part of this upgrade as shown in figure 1. Four rf signal synthesizers are used to provide the necessary rf signals for stand–alone or coupled operation. When running in stand-alone, each cyclotron and buncher combo utilizes its own pair. When operating in coupled mode, the K500 synthesizer pair provides the signals for both cyclotrons. Each synthesizer pair is locked together via a rear panel 10 MHz signal. It is important that they be locked together in this manner to reduce the phase noise in the phase detectors used as the feedback element in the phase regulation system. One synthesizer in each pair provides the cyclotron operating frequency(s) fed to the reference dee (K500-A and K1200-C) phase regulator while the other adds 2 MHz to the cyclotron frequency to generate the so-called "F+" signal used in the phase detectors.

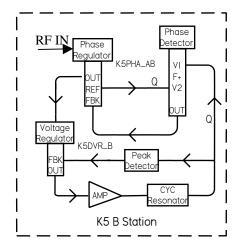

Figure 2 shows the typical signal flow diagram representative of all rf stations except for the K500-A and K1200-C beam injection stations. The "REF" output of the K500-A and K1200-C Phase Regulators feed distribution amplifiers (RF Buffer Amp) that distribute the rf signal to the other dees and buncher systems. Hence the phases of these other systems "ride" on the phase of the reference system. As mentioned, a complete signal flow diagram is displayed in figure 1.

Figure 2

Representative RF Station Signal Flow

A few words describing the signal flow displayed in figure 1 are appropriate. The amplitude and phase are independently controlled. The label "FBK" in the diagram stands for "Feedback". Both the amplitude and phase utilized analog feedback controls within the regulator modules to lock the value to that requested in the presence of both slow drifts – such as temperature – and fast disturbances – such as recovery from spark events and tuner movements. The phase loop is more complex than the amplitude loop since the phase detector must be synchronized to the system and this synchronization must be maintained in the presence of changes in requested value. To do this the phase regulator module provides two outputs "OUT" and "REF". During system setup

following a frequency change, an offset between the OUT and REF outputs is established that synchronizes the phase detector to operate about zero with the proper slope polarity for stable operation. Internally, the rf signal used to feed the REF and OUT controls are fed from the operator phase control section. In this manner the OUT and REF are locked to the requested phase value so that changes in requested phase settings do not effect the system synchronization.

## **Module Specifications**

Three modules support the signal distribution and phase control. The modules are the 1) RF Buffer Amp, 2) RF Phase Detector, and 3) RF Phase Regulator. A basic description and schematic diagram will be presented here for each module in turn.

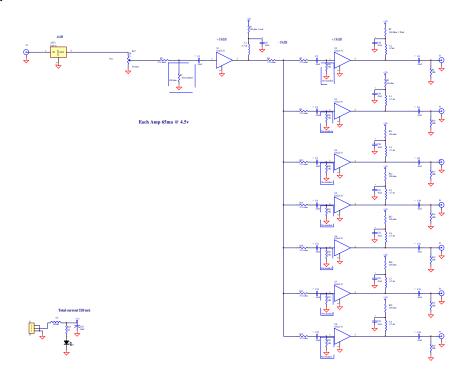

### RF Buffer Amp

The unit is packaged in a single-wide NIM module containing a single pc board. The module is documented in NSCL bundle # 11. Figure 2 displays the RF Buffer Amp schematic. As can be seen, the amplifier takes a single input and distributes it to seven outputs. The gain from input to output is common to all outputs and is adjustable from 0 to 6 dB with a front panel accessible pot designated R27 on the drawing. This corresponds to a voltage gain of 0 to 2. The input and each output is matched to 50 Ohms.

Figure 3

RF Buffer Amp Schematic: # 011-0060-01-01\_00

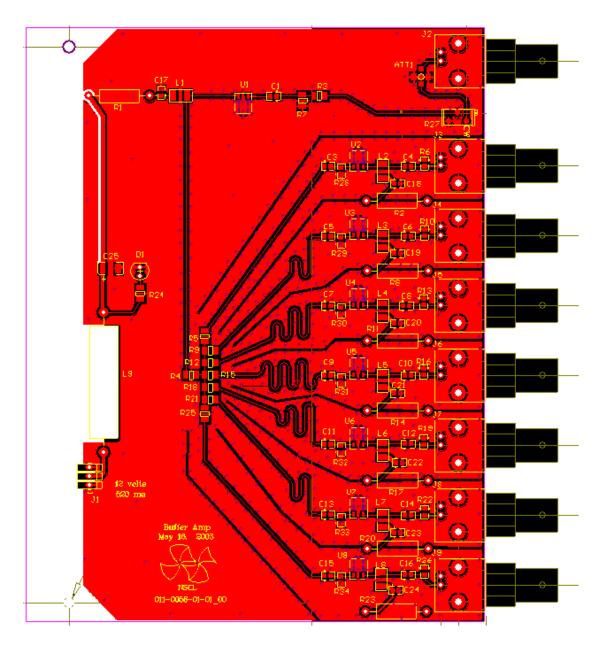

Figure 4 RF Buffer Amp PCB

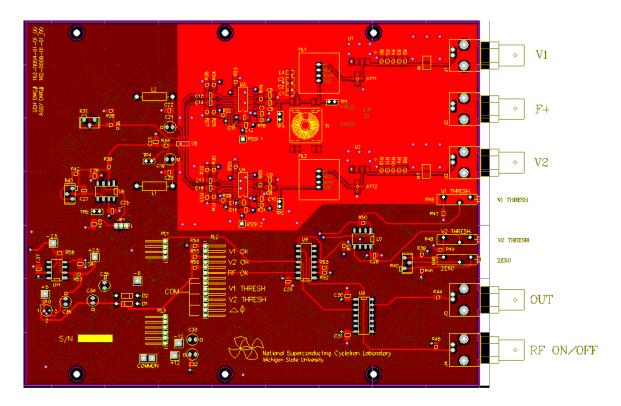

### RF Phase Detector

The unit is packaged in a single-wide NIM module containing a single pc board. The module is documented in NSCL Electronics Department bundle # 162. Figure 3 displays the RF Phase Detector schematic. The module accepts three rf input signals. The V1 and V2 inputs are matched to 50 Ohms and accept rf input signals with amplitudes from -20 dBm to +33dBm. The F+ input is matched to 50 Ohms and accepts a +13dBm amplitude input that is 2 MHz higher frequency than the V1 and V2 input. The module mixes the F+ signal with each signal input and filters the result to create clean 2 MHz IF signals that are processed against each other for phase detection. This "heterodyne" technique allows us to use the same filter at all frequencies to remove noise and harmonics as well as provide for a response and calibration that is independent of frequency. One of the 2 MHz IF's is shifted by 90 degrees to force the phase detector to operate about 0 volts for 0 phase. The output varies linearly from -9V at -90 degrees to +9V at + 90 degrees. The output response is flat to 300 KHz. In addition to the phase monitor output, the detector also provides digital "RF OK" outputs indicating that the rf is suppose to be on and both inputs have acceptable levels for reliable phase measurement.

Figure 5

RF Phase Detector Schematic: # 162-0004-01-01\_00

Figure 6 RF Phase Detector PCB Layout

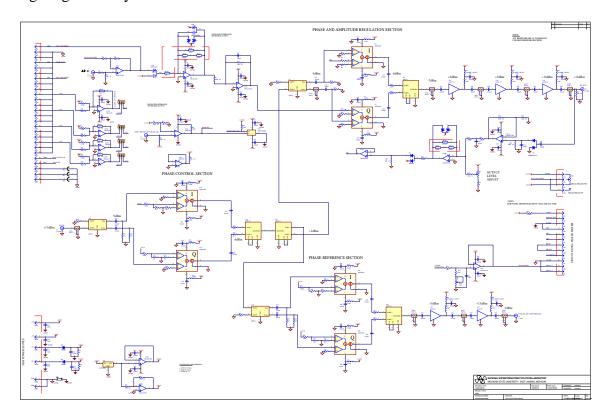

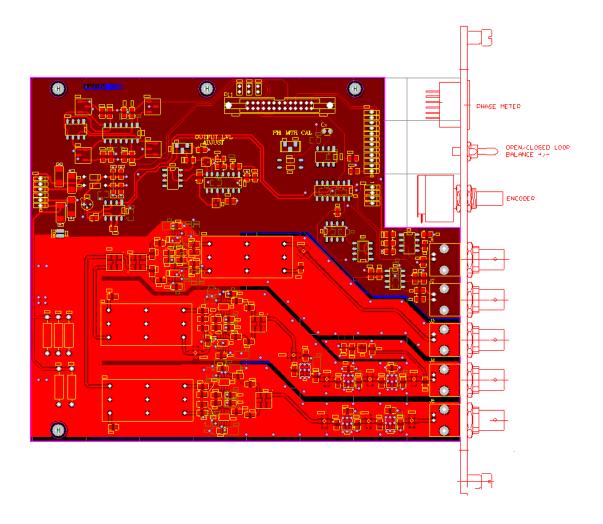

### RF Phase Regulator

The unit is packaged in a double-wide NIM module that contains three pc boards. The module is fully documented in Electronics Department bundle #162. The three boards include 1) the rf modulator, 2) the control interface, and 3) the Zworld embedded controller. The specific circuits of the Zworld controller and control interface board will not be discussed further since the circuits are either rudimentary or commercially documented. The rf modulator is the main board of this module and is described.

| Signal Label   | Signal                                |

|----------------|---------------------------------------|

|                |                                       |

| BEAM OFF       | 0 VDC = 45 degree shift from nominal  |

| ΔΦ ΙΝ          | -10 to +10 VDC phase error signal     |

| RF IN          | 7 to 13 dBm, 2 to 32 Mhz, RF input    |

| RF OUT         | 13 dBm, 2 to 32 Mhz, RF main output   |

| RF REF         | 7 dBm, 2 to 32 Mhz, RF ref output     |

| RF OK          | +5 VDC=RF OK signal fm phase detector |

| PHASE METER IN | Scalable VDC input from phase meter   |

| EN             | 10-Base-T Ethernet control interface  |

The rf modulator board is basically an arrangement of three identical 4-quadrant linear I/Q modulators that may be though of as the 1) Phase adjust, 2) Synchronization adjust, and 3) Regulator modulators. The Phase adjust and Synchronization adjust modulators are controlled by the four DAC outputs of the Zworld controller, while the regulator modulator uses analog feedback loops to maintain the module output amplitude and lock the system phase. The regulator modulator maintains the module output amplitude by modulating the I-port and the system phase by modulating the Q-port. The I-port control is limited to positive values, hence the regulation I/Q modulator basically controls the position of a constant amplitude vector in the right half of the complex plane. The amplitude of the vector is held constant by the I-port control using feedback from an internal peak detector while the system phase is held constant by modulating the Q-port using feedback from an external system phase detector.

The rf flows through the module first passing through the Phase adjust modulator and is then split with one signal passed through the Synchronization adjust modulator and the other passed through the Regulator modulator. In this arrangement, the system synchronization and regulation ride on the phase command so that a change in the requested phase does not adversely affect synchronization or regulation. With the current 12-bit Zworld based controller, the phase is adjustable in < 0.1 degree steps. The system phase and module amplitude regulation is analog so that stability is not dependent on digital granularity.

Figure 7

RF Phase Regulator Schematic: # 162-0018-01-01\_00

Figure 8 RF Phase Regulator PCB Layout

The internal controller is interfaced to the module controls in the following manner.

#### **Digital Inputs:**

```

Di00: Optical Encoder Signal 1 (A)

Di01: Optical Encoder Signal 2 (B)

```

Di02: Calibrate switch (5V = Knob -> Ao00, Ao01, 0V = Knob -> Ao02, Ao03)

Di03: RF1 OK Status (5V = RF1 OK)Di04: RF2 OK Status (5V = RF2 OK)Di05: Beam Off (5V = Beam is Off)

Di06: Open/Closed pushbutton (0V = change/toggle open/closed loop mode)

Di07: Coarse/Fine adjustments (0V = Coarse, 5V = Fine)

### **Digital Outputs:**

```

Do00: Activity LED

Do01: Balance + LED

Do02: Balance -- LED

Do03: RF OK LED

Do04: Beam Off LED

(0V, LED on, if Error > +MaxErr)

(0V, LED on, if Error < - MaxErr)

(0V, LED on, if Di03,Di04 = 5V)

```

Do05: Open/Closed Loop (0V if (Closed Loop requested) and (RF1&2 OK))

Do06: Calibration Running (0V = calibration being run)

Do07: Locked (0V = Locked = Closed Loop & Balanced – blink if unbal)

### **Analog Inputs:**

Ai00: delta-theta Error (9V = 90 degrees) Ai01: theta meter read (10V = 180 degrees) Ai02: delta-theta Offset (9V = 90 degress)

### **Analog Outputs:**

Ao00: Ctl/Set I = 10 \* Cos(-theta ctl/set) Ao01: Ctl/Set Q = 10 \* Sin(-theta ctl/set) Ao02: Ref/Cal I = 10 \* Cos(-theta ref/cal) Ao03: Ref/Cal Q = 10 \* Sin(-theta ref/cal)

The Ethernet based control interface uses the standard Modbus over Ethernet protocol. The module responds to the following Modbus addresses.

(reg #'s marked with #F are IEEE-754 32-bit floats and require 2 regs)

| 00001<br>00002<br>00003                            | DoReboot<br>DoInit<br>KillTeInet                                                   |                                                                                                                                                                                                                              |

|----------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00021<br>00022<br>00023<br>00024<br>00025<br>00026 | CalibCtlSet<br>CalibRefCal<br>ToggleLoop<br>HdwOverride<br>ResetMap<br>ToggleLocal | Calibrate (map) Ctl/Set to Meter values Calibrate Ref/Cal for a good lock Invert open/closed loop (lock) mode Enable ability to override hdw read bits (disabled) Reset Ctl/Set-to-Meter values map Toggle Local/Remote mode |

| 30051                                              | CtlrState CS_REFCAL_CALIB CS_CTLSET_CALIB CS_HDW_OVERRIDE CS_HDW_ERROR             | bit-arrary of controller state<br>0x0001<br>0x0002<br>0x0004<br>0x0008                                                                                                                                                       |

| CS_BA<br>CS_BA<br>CS_RF<br>CS_RF<br>CS_BE |                                         | 0x0010<br>0x0020<br>0x0040<br>0x0080<br>0x0100<br>0x0200<br>0x0400                                                                      |

|-------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 40001#F<br>40003#F<br>40005#F<br>40007#F  | In0<br>In1<br>In2<br>In3                | Raw Input Voltage 0 (diagnostic) Raw Input Voltage 1 (diagnostic) Raw Input Voltage 2 (diagnostic) Raw Input Voltage 3 (diagnostic)     |

| 40009#F<br>40011#F<br>40013#F<br>40015#F  | Out0<br>Out1<br>Out2<br>Out3            | Raw Output Voltage 0 (diagnostic) Raw Output Voltage 1 (diagnostic) Raw Output Voltage 2 (diagnostic) Raw Output Voltage 3 (diagnostic) |

| 40017#F<br>40019#F                        | ThetaCtlSet<br>ThetaRefCal              | Control/Set angle in degrees<br>Reference/Calibration (sync) angle in degrees                                                           |

| 40021<br>bits)                            | DigStatus                               | Status bits (copy of 8 least significant digital Input and Output                                                                       |

| 40022#F<br>40024#F<br>40026#F             | ThetaOffset<br>ThetaError<br>ThetaMeter | Theta Offset in degrees Theta Error in degrees Theta Meter reading in degrees                                                           |

| 40028#F<br>40030#F                        | CtlSet_I<br>CtlSet_Q                    | I-component of Control/Set angle<br>Q-component of ControlSet angle                                                                     |

| 40032#F<br>40034#F                        | RefCal_I<br>RefCal_Q                    | I-component of Control/Set angle<br>Q-component of Control/Set angle                                                                    |

| 40036#F<br>(diagnostic)                   | NeededCtlSet                            | angle needed to achieve ThetaCtlSet value on ThetaMeter                                                                                 |

| 40038#F<br>40040#F                        | KnobRate1<br>KnobRate2                  | coarse chg rate for Ctl/Set or Ref/Cal (in degrees/knob turn) fine chg rate for Ctl/Set or Ref/Cal (in degrees/knob turn)               |

| 40042#U32<br>(disabled)                   | DigInOverride                           | 16-bit mask + 16-bit value for overriding digital I/O values                                                                            |

| 40044#F<br>Unbalanced                     | BalRange                                | # ThetaError degrees offset from 0 that is considered                                                                                   |

# **Summary and Concluding Statements**

The rf signal distribution and phase control system has been upgraded. The system now supports full 360 degree control and is optimized for coupled cyclotron operation. The "RF Frequency Generation and Distribution System" is described in NSCL Electronics Department bundle #11 and the "RF Phase Control System" is described in bundle #162. The documentation in the bundles should be referenced for detailed information beyond what is described here.